# Optimized Coding and Parameter Selection for Efficient FPGA Design of Attention Mechanisms

Computation output of 1<sup>St</sup> Tile

Ehsan Kabir, Austin R. J. Downey, Jason D. Bakos, David Andrews, Miaoqing Huang

# Introduction

- Deep neural networks (DNN) have shown significant advancements in natural language processing, machine translation, computer vision.

- An important feature named attention mechanism within any DNN enables a high level of computational parallelism for both the training and inference phases.

- Suitable for acceleration on hardware like FPGAs, due to FPGA's high degree of parallelism, low latency, and energy efficiency.

- We optimized high level synthesis (HLS) code to increase parallel DSP consumption.

- We introduced an efficient tiling technique and optimized the value of parameters within an attention layer to improve latency without exhausting computational and memory resources.

# Accelerating the Computation within the Attention Layer of a Neural Network

- A novel architecture to enhance parallel processing within the attention layer.

- An efficient coding in HLS to ensure high utilization of DSPs.

- An efficient tiling of weight matrices to accommodate large models in on-chip memory.

- A theoretical model validating both predicted and experimental latency.

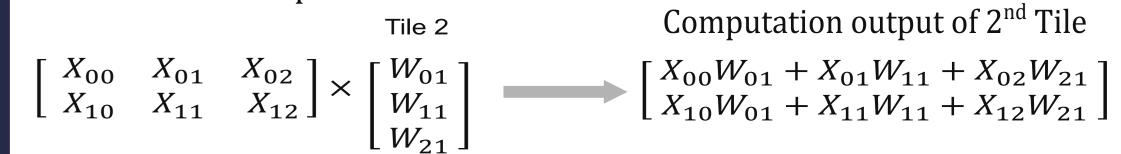

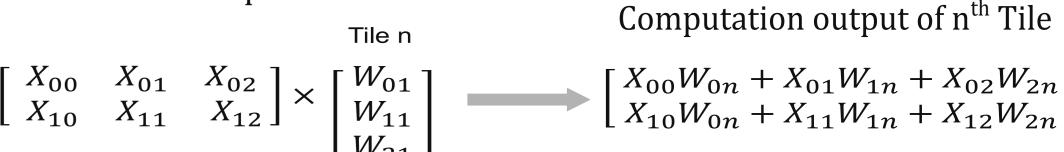

### Tiling Technique

| Load inputs into the Input BRAM                                                   |                                                         | Load Values of Each Tile into Weight BRAM                  |                            |                            |                            |                            |                                                                   |  |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|-------------------------------------------------------------------|--|--|

|                                                                                   |                                                         | Tile 1                                                     | Tile 2                     | Tile 3                     | Tile 4                     | Tile 5                     | Tile 6                                                            |  |  |

| $\left[ \begin{array}{cc} X_{00} & X_{01} \\ X_{10} & X_{11} \end{array} \right]$ | $\begin{bmatrix} X_{02} \\ X_{12} \end{bmatrix} \times$ | $\begin{bmatrix} W_{00} \\ W_{10} \\ W_{20} \end{bmatrix}$ | $W_{01} \ W_{11} \ W_{21}$ | $W_{02} \ W_{12} \ W_{22}$ | $W_{03} \ W_{13} \ W_{23}$ | $W_{04} \ W_{14} \ W_{24}$ | $\left[egin{array}{c} W_{05} \ W_{15} \ W_{25} \end{array} ight]$ |  |  |

| 1 <sup>St</sup> Iteration: Computation with 1 <sup>St</sup> Tile                  |                                                         |                                                            |                            |                            |                            |                            |                                                                   |  |  |

$\begin{bmatrix} X_{00} & X_{01} & X_{02} \\ X_{10} & X_{11} & X_{12} \end{bmatrix} \times \begin{bmatrix} W_{00} \\ W_{10} \end{bmatrix} \longrightarrow \begin{bmatrix} X_{00}W_{00} + X_{01}W_{10} + X_{02}W_{20} \\ X_{10}W_{00} + X_{11}W_{10} + X_{12}W_{20} \end{bmatrix}$ 2<sup>nd</sup> Iteration: Computation with 2<sup>nd</sup> Tile

n<sup>th</sup> Iteration: Computation with n<sup>th</sup> Tile

Final Matrix = Output for 1<sup>st</sup> tile + Output for 2<sup>nd</sup> tile + .....+ Output for n<sup>th</sup> tile

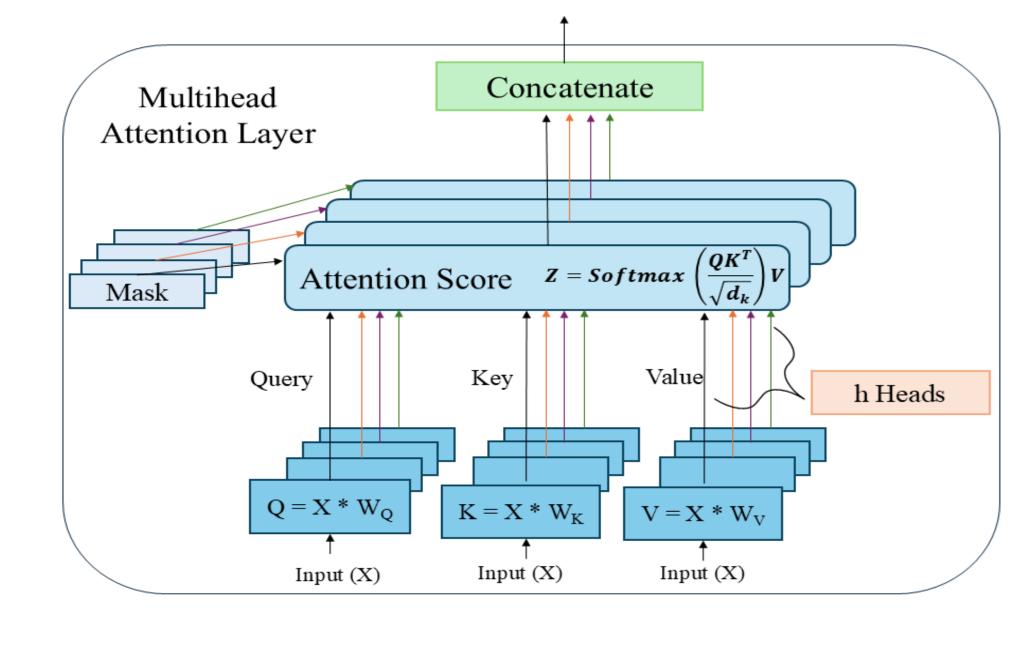

# Background

The input sequence X is linearly mapped into Query (Q), Key (K), Value (V) matrices using weights and biases. The parameter dk = dmodel/h is the 2nd dimension of Q and K. dmodel is a hyperparameter called embedding dimension and h is number of heads.

### Accelerator Architecture for Attention Mechanism

## Algorithm 4 Q, K, V Calculation Algorithm 2 Load Weights : for $(i = 1; i \le \frac{Embedding\ Dimension}{Number\ of\ Heads}; i = i + 1)$ do : for $(i = 1; i \le Sequence\ Length; i = i + 1)$ do #pragma HLS pipeline off

HLS Design Technique

for  $(k = 1; k \le \frac{d_{model}}{k}; k + +)$  do #pragma HLS pipeline II = 1 for  $(j = 1; j \le Tiles; j + +)$  do  $S_q \leftarrow S_q + x[i][j] \times w_q[k][j];$  $S_q \leftarrow S_q + x[i][j] \times w_k[k][j];$  $S_q \leftarrow S_q + x[i][j] \times w_v[k][j];$  $Q[i][k] \leftarrow Q[i][k] + S_q;$  $K[i][k] \leftarrow K[i][k] + S_k;$  $V[i][k] \leftarrow V[i][k] + S_v;$

17: **end for**

#### #pragma HLS pipeline off for $(j = 1; j \le Tiles; j = j + 1)$ do #pragma HLS pipeline II = 1 $w_q[i][j] \leftarrow weights\_Q[index];$ $w_k[i][j] \leftarrow weights\_K[index];$ $w_v[i][j] \leftarrow weights\_V[index];$ $index \leftarrow index + 1;$ 10: **end for Algorithm 3** Load Biases 1: for $(i = 1; i <= \frac{Embedding\ Dimension}{Number\ of\ Heads}; i = i + 1)$ do #pragma HLS pipeline II = 1 $q[i] \leftarrow bias\_Q[index];$ $b_k[i] \leftarrow bias\_K[index];$ $b_v[i] \leftarrow bias\_V[index];$ $index \leftarrow index + 1;$ 7: end for

# **Analytical Model**

$LI = [(d_{model} - 1) \times 1 + PD\_L] \times SL$  $LB = \left(\frac{d_{model}}{L} - 1\right) \times 1 + PD\_L$  $LIA = [(TS - 1) \times 1 + PD\_L] \times SL$  $LWA = \left[ \left( \frac{d_{model}}{L} - 1 \right) \times 1 + PD_{L} \right] \times SL$  $SA = \left[ \left( \frac{d_{model}}{b} - 1 \right) \times 1 + PD\_MHA \right] \times SL$  $BA = \left[ \left( \frac{d_{model}}{L} - 1 \right) \times 1 + PD\_BA \right] \times SL$  $S = [(SL - 1) \times 1 + PD\_S] \times SL$  $SV = \left[ \left( \frac{d_{model}}{l} - 1 \right) \times 1 + PD\_SV \right] \times SL$ No. of  $DSPs = 9 \times h + 3 \times h \times TS + 2 \times SL \times h +$  $2 \times d_{model}$  $LAT_{total}(cc) = LI + LB + LIA + LWA +$ SA + BA + S + SV $LAT_{total}(cc) \times 10^3$  $LAT_{total}(ms) = 1$ Frequency (Hz)

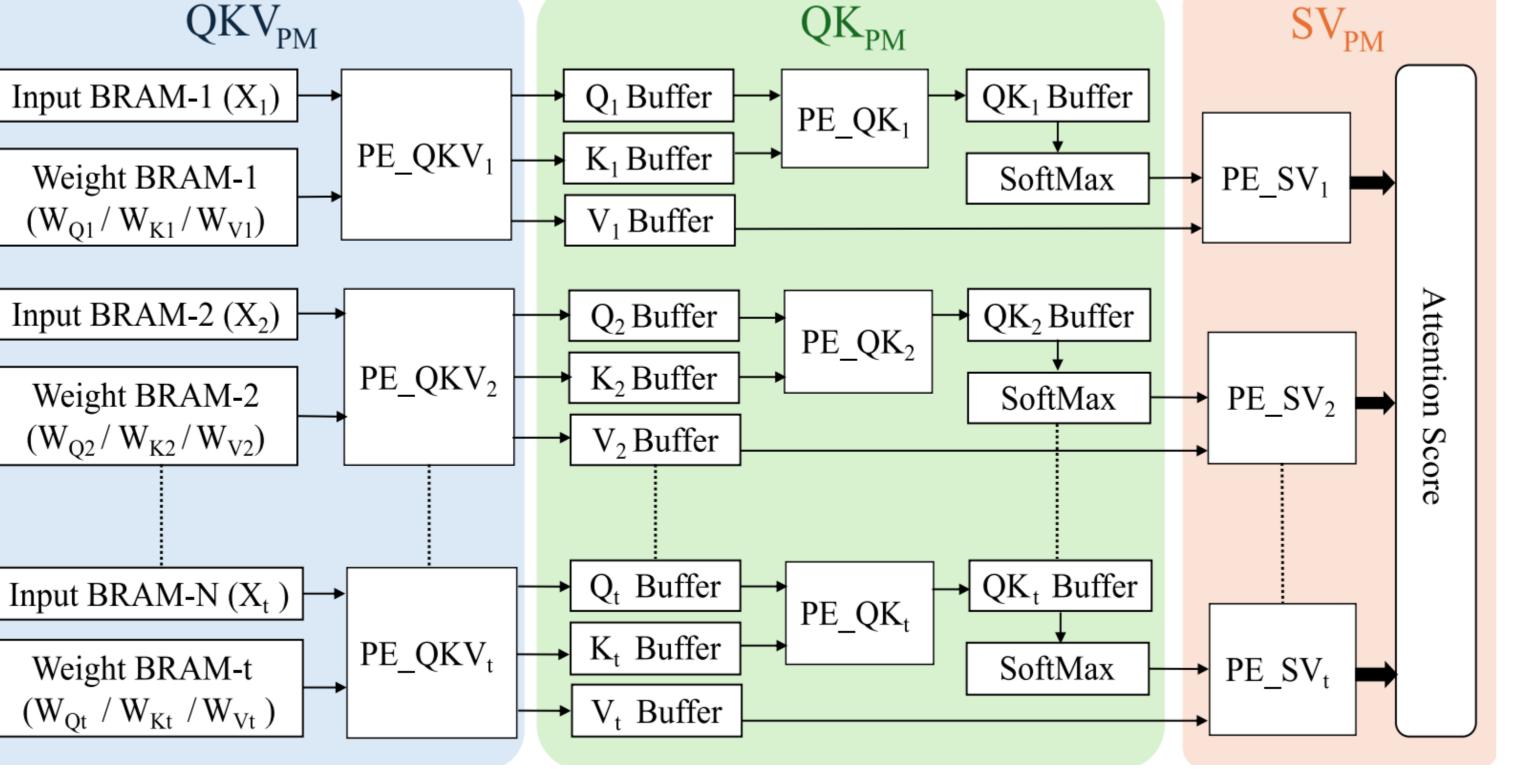

# Accelerator Architecture

- Designed with C in Vitis HLS.

- Three main processing modules:QKV<sub>PM</sub>, QK<sub>PM</sub> and  $SV_{PM}$ . QKV<sub>PM</sub>: Generates Q, K, V matrices. QK<sub>PM</sub>: Matrix-matrix multiplication operations between the Q and K matrices.

- SV<sub>PM</sub>: Matrix-matrix multiplication operations with V and the output from  $QK_{PM}$ .

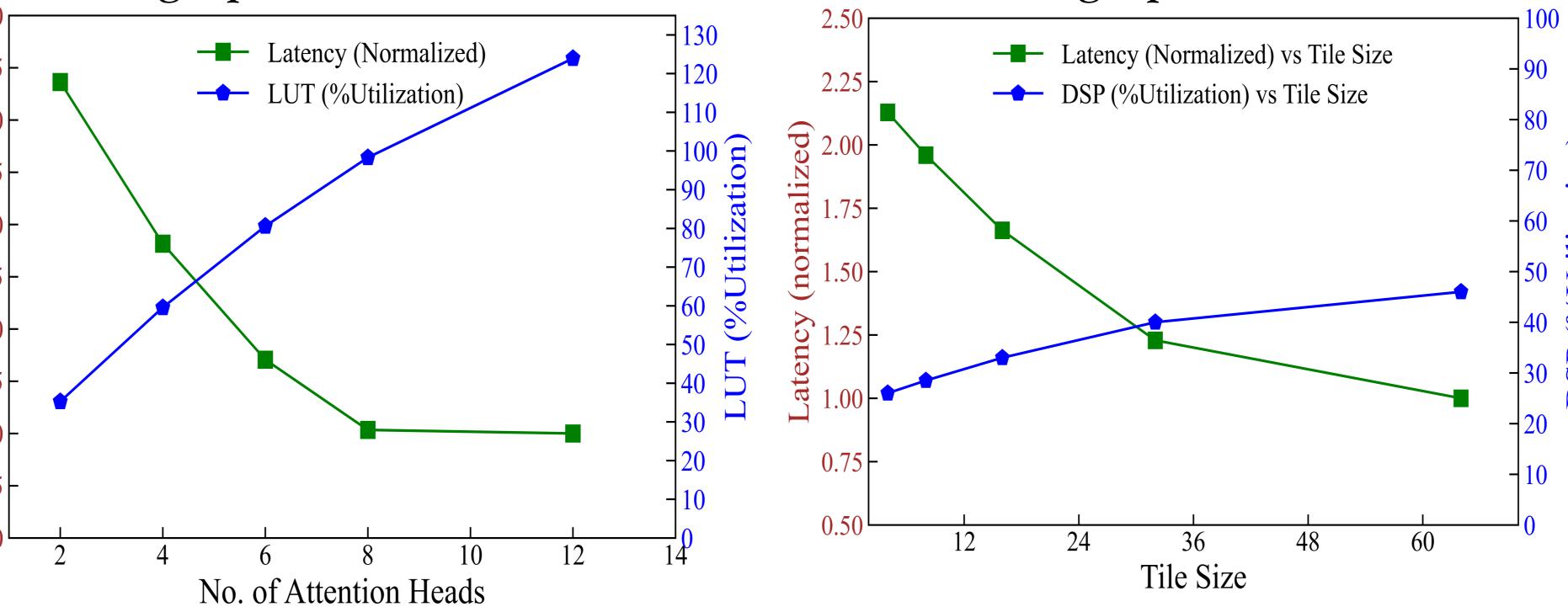

#### Choosing Optimum Head Number **Choosing Optimum Tile Size**

## Validation of Experimental and Analytical Results

| validation of Experimental and Analytical Results |                    |                        |                    |              |      |                    |                |  |  |

|---------------------------------------------------|--------------------|------------------------|--------------------|--------------|------|--------------------|----------------|--|--|

| Method                                            | Sequence<br>Length | Embedding<br>Dimension | Number of<br>Heads | Tile<br>Size | DSL2 | Frequency<br>(MHz) | Attention (SA) |  |  |

| Experimental                                      | 6.1                | 768                    | 8                  | 64           | 4157 | 400                | 0.94           |  |  |

| Analytical                                        | 64                 |                        |                    |              | 4168 |                    | 0.98           |  |  |

| Experimental                                      | 22                 | 768                    | 8                  | 64           | 3898 |                    | 0.534          |  |  |

| Analytical                                        | 32                 |                        |                    |              | 3656 |                    | 0.579          |  |  |

| Experimental                                      | 6.1                | 512                    | 8                  | 64           | 3887 |                    | 0.597          |  |  |

| Analytical                                        | 64                 | 512                    |                    | 04           | 3656 |                    | 0.592          |  |  |

#### References

- [1] E. Kabir et al., "Accelerating lstm-based high-rate dynamic system models," in FPL Conference, 2023.

- [2] B. Li et al., "Ftrans," in International Symposium on Low Power Electronics and Design, 2020.

- [3] E. Kabir et al., "Protea," in SC24-W: Workshops, 2024.